EN0-001 ARM Accredited Engineer Free Practice Exam Questions (2026 Updated)

Prepare effectively for your ARM EN0-001 ARM Accredited Engineer certification with our extensive collection of free, high-quality practice questions. Each question is designed to mirror the actual exam format and objectives, complete with comprehensive answers and detailed explanations. Our materials are regularly updated for 2026, ensuring you have the most current resources to build confidence and succeed on your first attempt.

Which of the following is an advantage of the single-step debug technique?

When linking with the standard C library, which library functions MUST be redefined in order to port your code to a new piece of production hardware?

Which of the following functions can be performed by a spinlock?

It is common to declare structures as "packed" in order to minimize data memory size. Which of the following accurately describes the effect of this?

Under which of the following circumstances is TLB maintenance always required?

In which of the following situations would you use a mutex to avoid synchronization problems?

Implementing loops using a decrementing counter which exits the loop when a counter reaches zero can be beneficial for power and performance. This is because:

Which ARMv7 instructions are recommended to implement a semaphore?

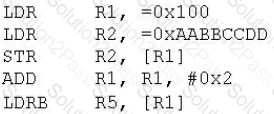

Assume a little-endian system.

What is the value of R5 after the execution of the following piece of code?

Literal pool loads to access constants at run-time can be minimized by:

How many bytes of stack are needed to pass parameters when calling the following function?

int foo( short arg_a, long long arg_b, char arg_c, int arg_d )

Which THREE of the following items should be preserved by software when entering dormant mode? (Choose three)

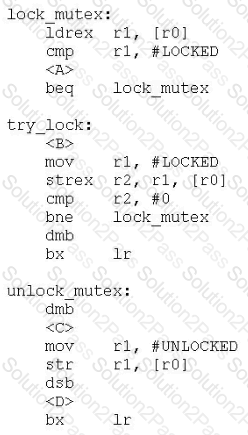

The following pair of functions implement a simple mutex spinlock which might be used to protect a critical code section in a multi-threaded application. The address of the lock variable is in r0.

In order to minimize power while waiting for the lock to be available. SEV and WFE instructions can be used to place the processor in a low power state while waiting for the lock to become available. At which points should these instructions be placed?

Using a Generic Interrupt Controller (GIC), when the interrupt handler writes to the End of Interrupt Register (ICCEOIR), which of the following state transitions might occur for that interrupt ID?

Which of these items is typically shared between threads running in the same Operating System (OS) process?

Cortex-A series processors contain event counting hardware which can be used to profile and benchmark code. The counters for these are programmed using:

When setting the initial location of the stack pointer and the base address of the heap, the ARM EABI requires that the:

A standard performance benchmark is being run on a single core ARM v7-A processor. The performance results reported are significantly lower than expected. Which of the following options is a possible explanation?

Which of the following processor resources do NOT have to be saved or modified by the Linux scheduler during context switch?

Which of the following techniques can be used to obtain a precise count of clock cycles when profiling software over an arbitrarily long period of time using the Performance Monitoring Unit?