EN0-001 ARM Accredited Engineer Free Practice Exam Questions (2026 Updated)

Prepare effectively for your ARM EN0-001 ARM Accredited Engineer certification with our extensive collection of free, high-quality practice questions. Each question is designed to mirror the actual exam format and objectives, complete with comprehensive answers and detailed explanations. Our materials are regularly updated for 2026, ensuring you have the most current resources to build confidence and succeed on your first attempt.

In an operating system environment, most applications are executed in which processor mode?

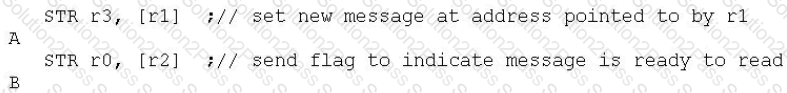

A message passing system between two CPUs is implemented using data stored in a shared area of memory. To pass a message, the first CPU executes the instructions:

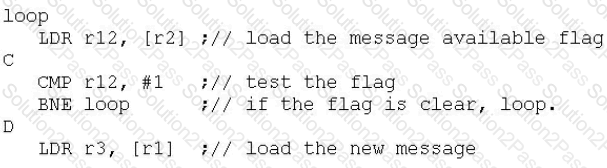

The second CPU receives the message using the instructions:

On both CPUs, r1 = 0x5000 and r2 = 0x6000. At which of the points A, B, C and D must Data Memory Barrier (DMB) instructions be placed in order to ensure messages are passed reliably and efficiently?

In which of the following scenarios would cache maintenance operations be necessary in an ARMv7 system?

Which instruction would be used to return from a Reset exception?

In Architecture ARMv7-A which one of the following has a known physical address at power-on reset?

A 32KB 4-way set associative instruction cache supports a cache line size of 64 bytes. How many bits are required to index a cache line in a way?

Which of the following is an external exception?

On an ARM processor that does not implement Security Extensions, which one of the following can be the starting address of the exception vector table?

Which of the following is an accurate description of network storage as compared to on-chip RAM?

When building code for both ARM and Thumb states, which tool decides for each function call whether to use a BL or BLX instruction?

A development board is supplied with a Board Support Package (BSP) for a particular operating system. Which TWO of these items would you expect to find in the BSP? (Choose two)

According to the AAPCS (with soft floating point linkage), when the caller "func" calls sprintf, where is the value of the parameter "x" placed?

#include

void func(double x, int i , char *buffer)

{

sprintf(buffer, "pass %d: value = %f\n", i, x); }

What view in a debugger displays the order in which functions were called?

Which of the following memory attributes, specified in a translation table entry, could be used to protect a page containing a read-sensitive peripheral from speculative instruction fetches?

An Advanced SIMD intrinsic has the prototype:

int16x4_t vmul_n_s16(int16x4_t a, int16_t b);

How many multiplications does this intrinsic compute?

A simple method of measuring the performance of an application is to record the execution time using the clock on the wall or a wristwatch.

When is this method INAPPROPRIATE?

Is it possible to use an interrupt controller based on the Generic Interrupt Controller (GIC) architecture in a device built around a single core Cortex-A9 MPCore processor?

The Q-flag in the program status register (PSR) indicates which of the following?

An embedded application running on an ARM processor is not meeting its expected performance target. The target hardware on which the application is running allows the frequency of the CPU to be increased independently from the memory system.

The CPU frequency is increased from 800 MHz to 1 GHz and experiments verify that the application performance does not increase.

Which one of the following statements MUST BE TRUE?

As part of the ABI specification, the AAPCS defines which of the following?